PCB

电路基础

电路定理

KCL 基尔霍夫电流定律:流入的电流等于流出的电流

- 在集总参数电路中,任意时刻,对任意结点流出(或流入)该结点电流的代数和等于零

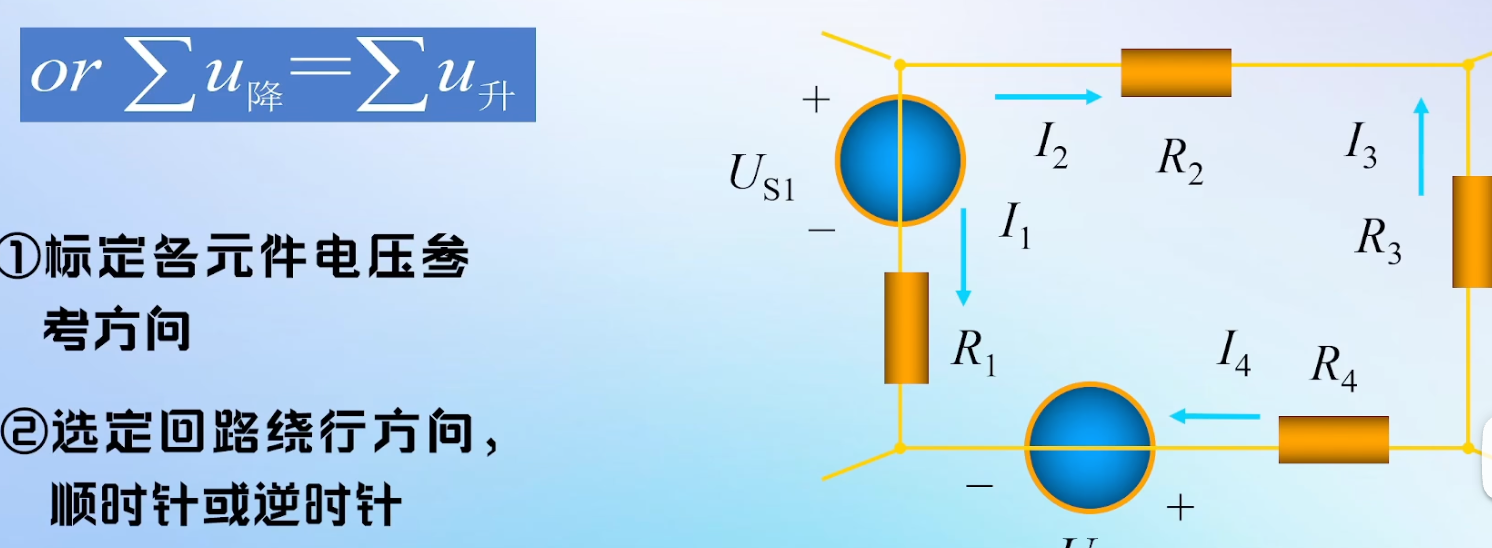

KVL 基尔霍夫电压定律

- 在集总参数电路中,任意时刻,沿任一回路,所有的支路电压代数和恒等于0

其他概念

- 集总参数电路:假定理想条件下,近似地描述实际电路,前提要求实际电路的尺寸要远小于电路工作时的电磁波的波长

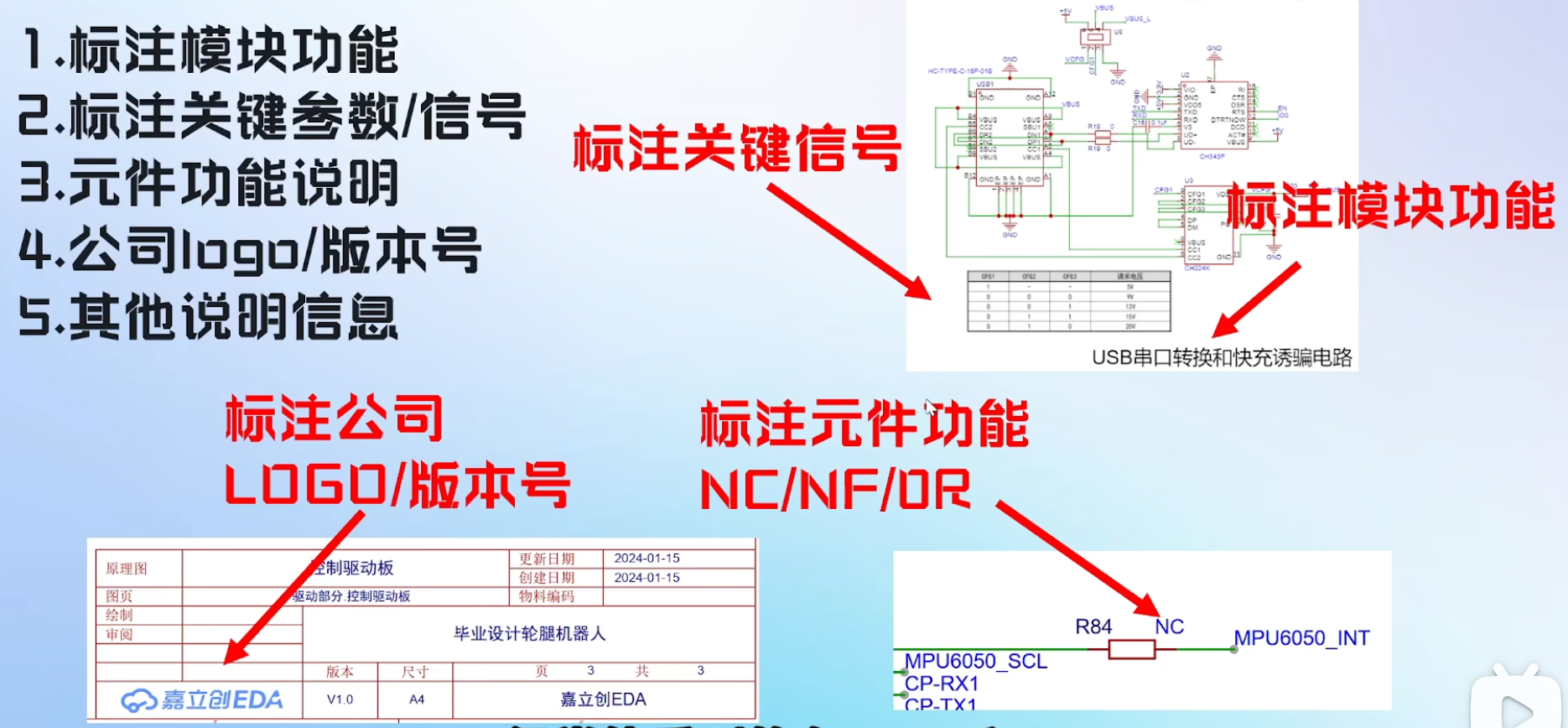

读懂原理图

注释

标注元件功能

shNC # no content 默认不链接 NF # no fix 默认不安装 0R # 可以短路连接1

2

3

基础入门

锡金属

- 熔点一般在183 °c左右

PCB设计

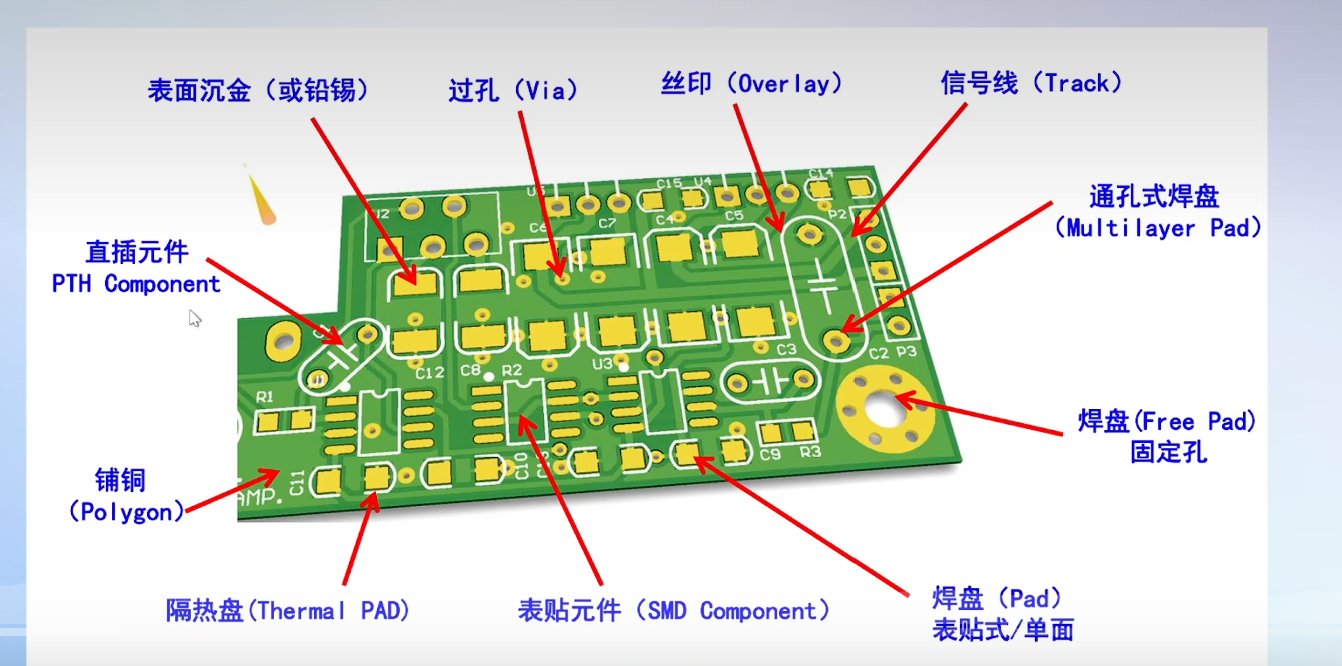

概述

- 导线:具有和原理图对应的网络连接关系;布线时,导线可被自动推挤、环绕等;通常用于信号线

- 铺铜:通过一整块铜皮对网络进行连接,通常用于地GND 和 电源POWER

- 十字隔热隔离设计,避免焊接时散热太快,利于焊接

- 填充-无任何隔离,一般用在需要过大电流时,如电源线的布线

- 丝印:PCB上印刷的信息,用于标识电子元件位置、数值、型号等信息;

- 阻焊:在铜层上覆盖油墨层,防止PCB上的线路与其他金属、焊锡或其他导电物体接触短路;起到绝缘和保护铜层作用;选择性漏出焊接需要的PAD、IC等

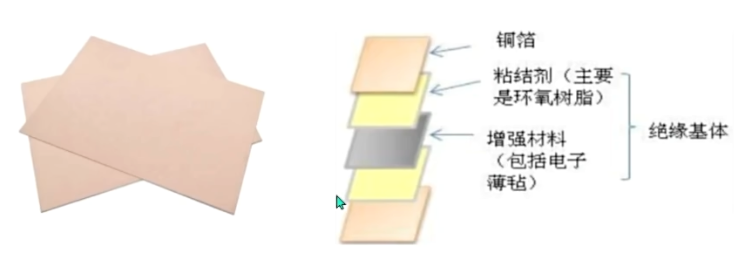

覆铜版

PCB制作的原料,覆铜板也称铜箔bó层压板,由一层或多层铜皮,粘着一块绝缘基材所组成的板子,通常以玻璃纤维居多。

制作流程

- 覆铜板 - PCB设计 - 钻孔 - 显影 - 蚀刻 - 阻焊涂层 - 保留焊盘 - 印制丝印 - 【焊盘和接口处理】

- 显影:按照设计的PCD线路图,将一种防腐蚀材料精确的印刷在覆铜板上

- 蚀刻:将覆铜板浸入特定化学溶剂,将未被抗腐蚀材料保护的铜溶解去除,精确地留下PCD导电铜路径

- 阻焊涂层:铜线长时间暴露在空气中就会老化、短路风险,因此在电路板上加一层绝缘图层,不同材料涂层的颜色可能不同,但不会存在性能差异

- 保留焊盘:铜板被阻焊涂层覆盖,电子元件将无法通过焊接,与其固定连接,对于预定安装电子元件的位置,必须移除相应区域的阻焊涂层

- 【焊盘和接口处理】:铜材料暴露容易氧化,导致性能下降,通常会进行抗氧化的二次处理,因此开发板上的盘并非同本身的黄色,而是呈现一种银白色,这是因为进行镀锡处理,保护铜焊盘的同时提高焊接的可靠性和耐久性;甚至镀金/银

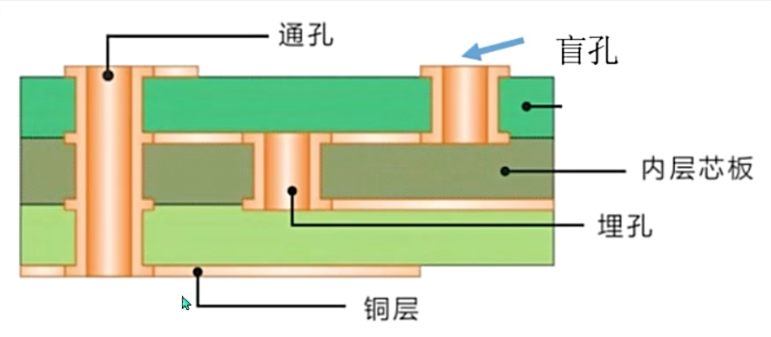

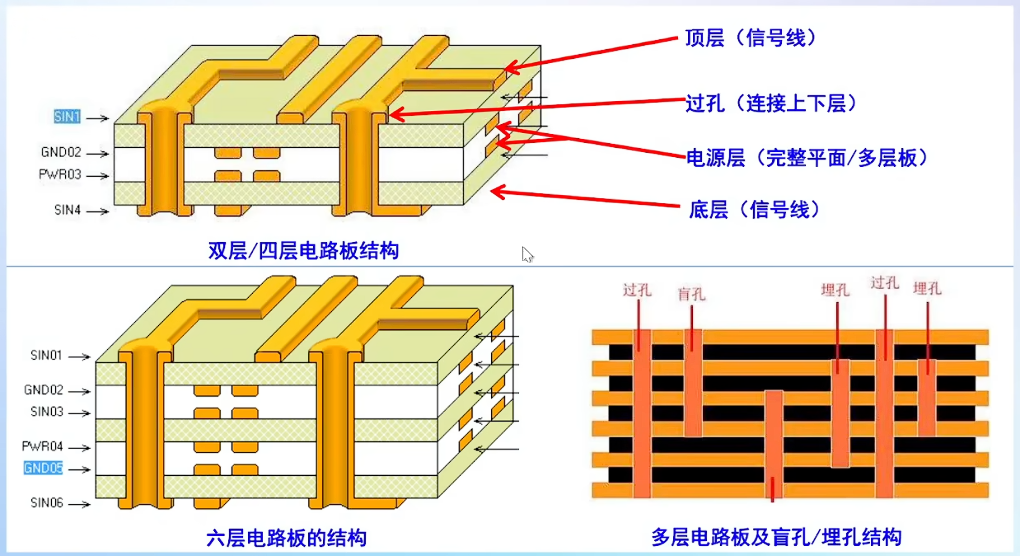

过孔

- 通孔 Through Hole:从PCD的一侧直接穿透至另一侧

- 盲孔 Blind Via:连接PCB内层与外层,但不贯穿整个PCB

- 盖孔 Buride Via:仅存在于PC B的内部层之间,不与PCB表层相连

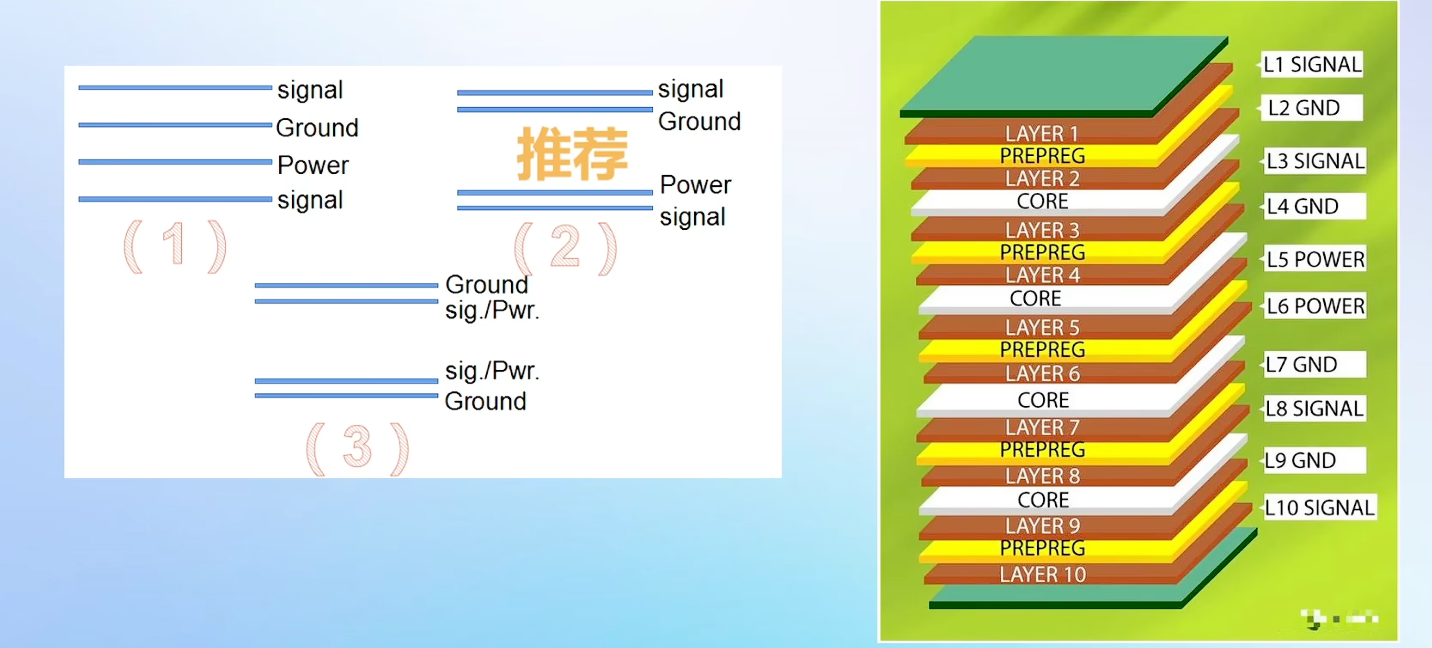

PCB叠层结构

电路板的层数通常以双层递增,如2、4、6层等;四层板可以被理解为由两个双层板通过夹持一层绝缘基材而组成。

- 信号层 Signal layer:包括顶层、底层、中间层;各层间可以通过过孔、埋孔、盲孔实现互相连接

- 丝印层

- 阻焊层

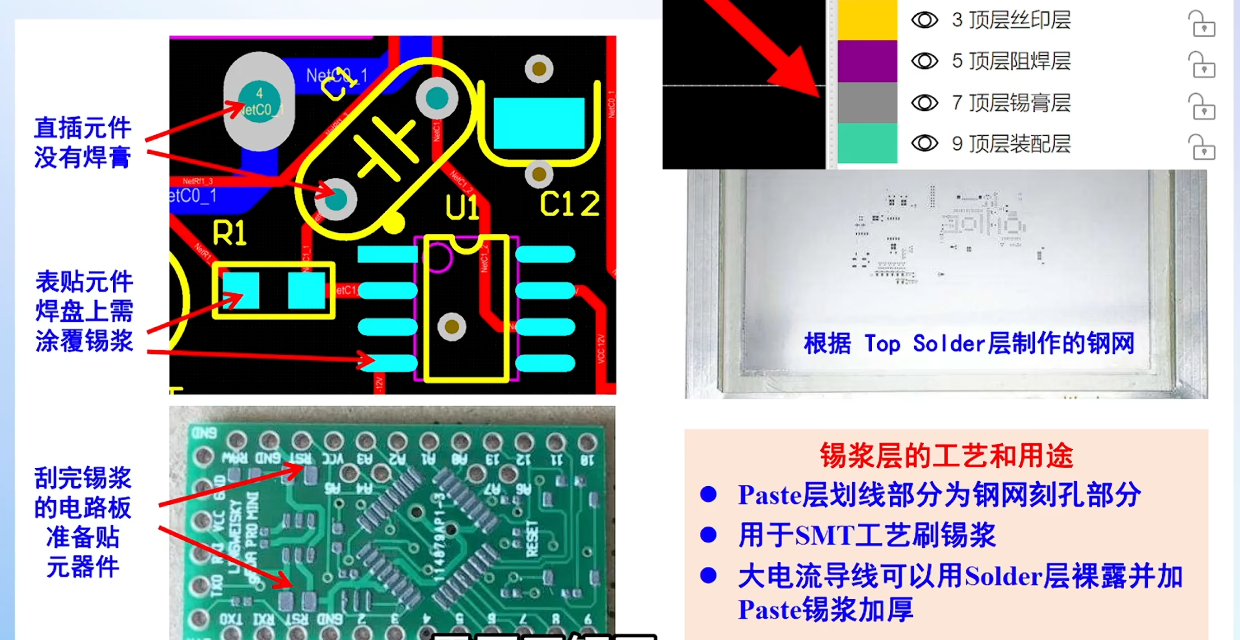

- 锡膏层:钢网是根据锡膏层进行对应开孔; 锡膏层会在回流焊时被涂上锡膏

- 多层:过孔一般要穿越多层,过孔中间的区域被称为多层;当希望不要铺铜到某一区域/禁止布线时会有这个多层选项,防止顶层和底层的铺通

- 机械层:定义整个PCB板的外观,用于设置电路板的外形尺寸,数据标记、对其标记、装配说明及其他的机械信息

- 板框层:控制板子的大小

- 3D外壳层:简单的PCB外壳

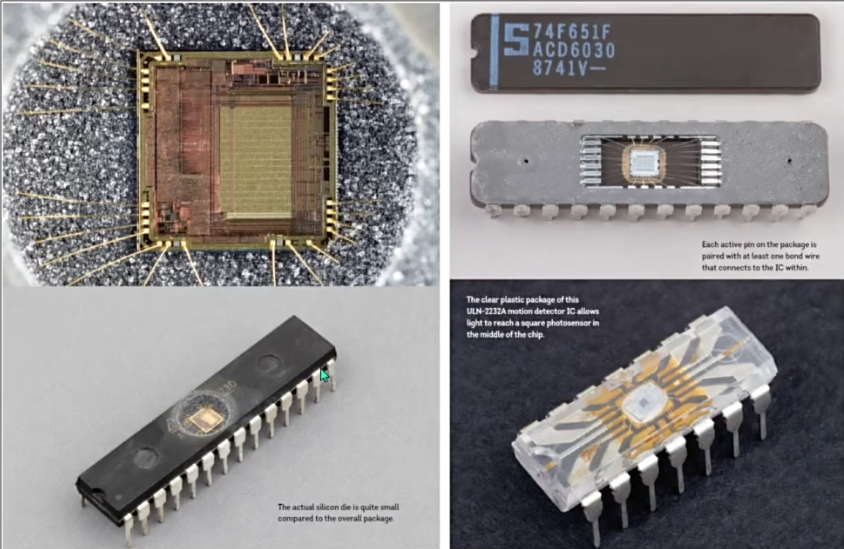

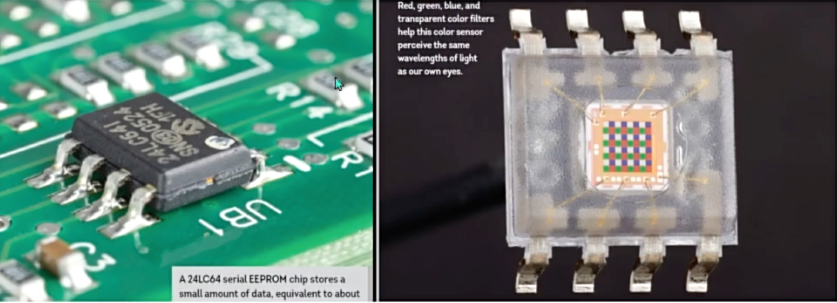

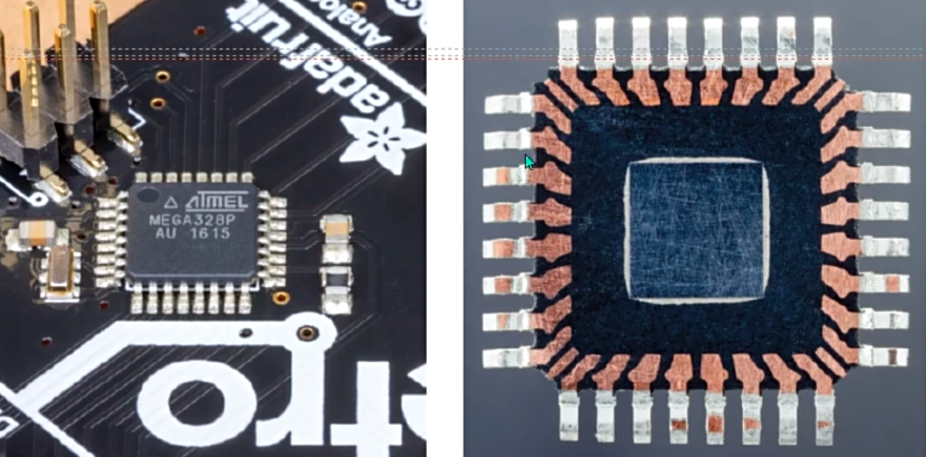

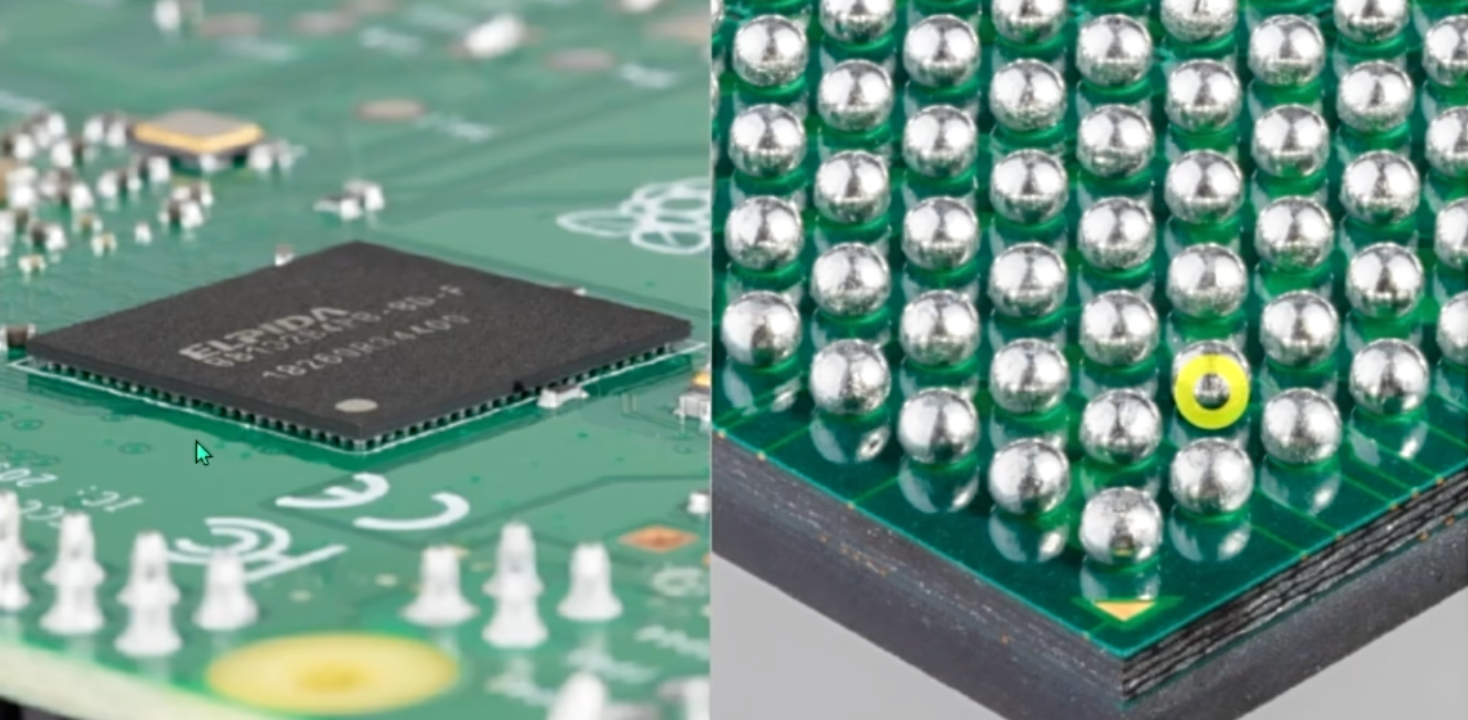

封装

将半导体芯片、集成电路、晶体管这样的电子部件用一种保护性的材料包起来,能够轻松的连接到电路板上。

- 分类

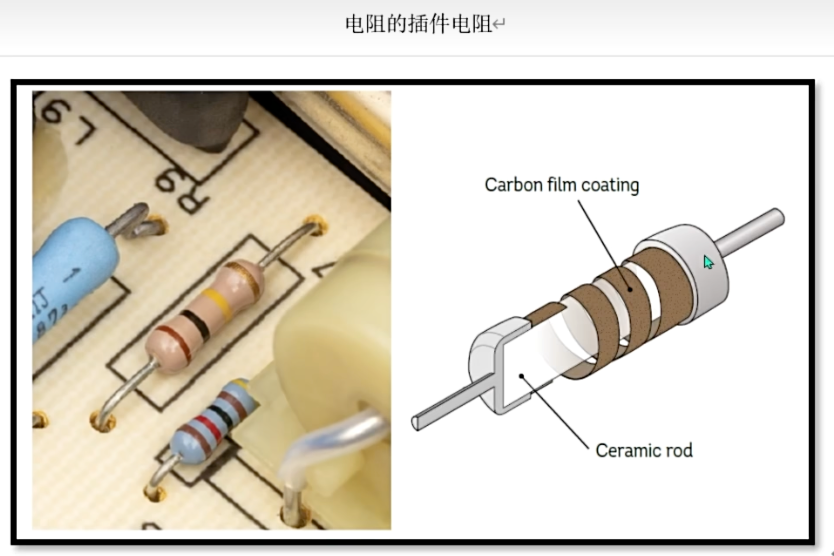

- 插件:

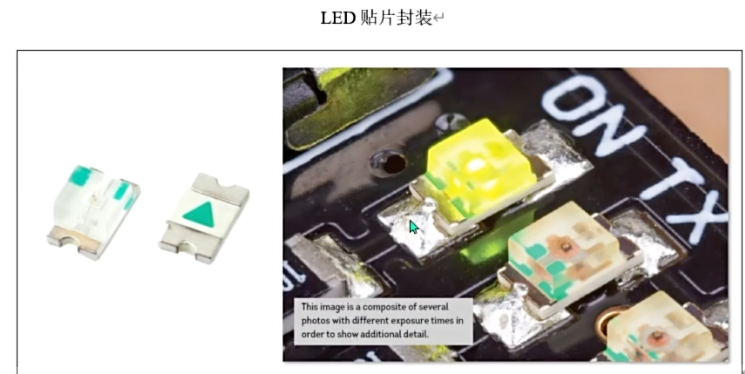

- 贴片

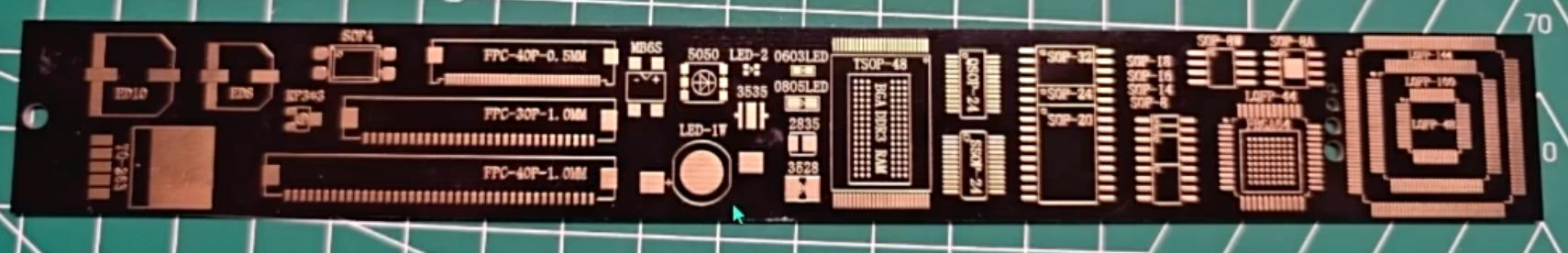

- 封装规范 - “信仰尺📏”

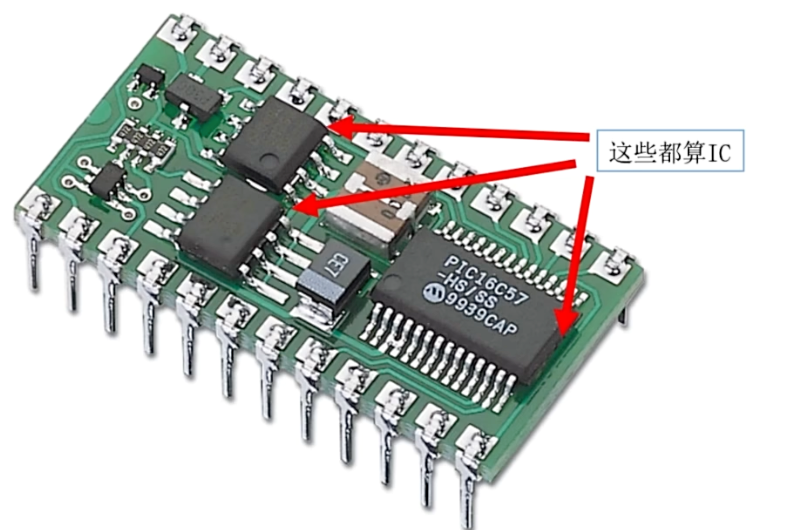

IC 芯片

- 集成电路 / IC 芯片(Integrated Circuit):内部嵌入了精密设计的复杂电路,包括晶体管,电阻,电容等基本电子元件

- 大多由半导体材料如硅制造而成,大的减小了电路的体积与成本,同时显著提升了电子设备的性能

DIP封装

DIP 双列直插封装,传统的封装形式,原件有两排平行的引角适合穿孔安装在PCB

SOIC封装

SOIC 小型轮廓封装:常用于贴片技术,与DIP封装类似,只是引角弯曲,需直接焊接在PCB上

QFP封装

QFP 四边扁平封装:四边都有引脚,用于集成电路提供较高的引脚数目,适合复杂的电路设计

BGA 球栅阵列封装

在元件底部使用网格形式的球形引脚,提供更高的引脚密度,使用高性能、多引脚的集成电路

元件封装绘制

PCB布局

布局要求

元器件之间应相互平行或者垂直排列,以求整齐、美观;元件排列紧凑,在整个版面上应分布均匀、疏密一致

对于非手动焊接,希望降低批量生产时回流焊工艺复杂度时,要求 所有元器件均放置在顶层;手工焊制无所谓

必须根据元器件电器特性和使用特点布局

- 各种接口、按键和排阵,需放在板子边缘,方便插接

- 对于屏幕、主控芯片等,一般放在板子中央

- 电源电路,一般放在板子的电源输入旁边,且要注意电流路径和滤波电容位置(非常重要)

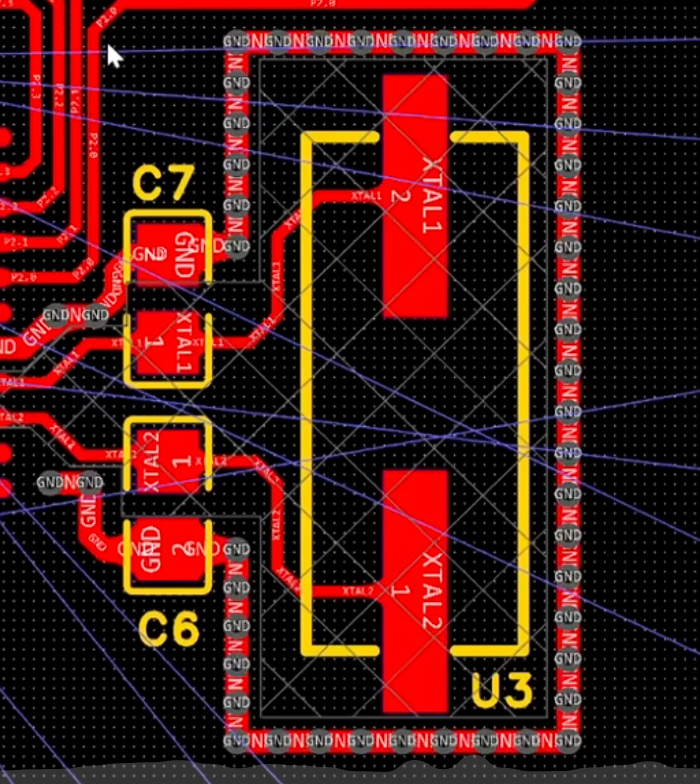

- 晶振需靠近单片机晶振引脚摆放

元器件是三维物体,空间干涉情况需单独考虑

元件的布局应采用模块化,也就是同一模块电路的元件应放同一区域,按就近原则布局

不要使用自动布线!!!

顶层优先原则:尽可能在顶层布线

电源线原则上要加粗:利于电流流通

- 日常PCB设计中,在25°c时,铜厚10z盎司的导线,10mil线款能够承载0.65A电流;40mil线宽能够承载2.3A电流

同一层内走线大于90°:同一层禁止走线90°或锐角,锐角/直角会造成走线阻抗不连续,影响信号的传输,推荐走线135°

注意电流路径和电容位置:电源应先经过电容滤波再传给后级,去耦电容要贴近芯片引脚放置,并就近接地

高频信号线应尽可能短,等距,并做好与其他信号线的屏蔽隔离。

为降低相邻走线间的串扰,尽量避免相邻层平行走线

走线应遵需3W原则:相邻层信号线应采用正交方向

晶振这类高频信号线,尽可能保证走线长度一致,差分线布线应尽量等距等长

借助布线-差分对布线功能实现-绘线过程中会动态提示

屏蔽信号实现:外围打一圈GND的过孔

在包裹的GND过孔内部,设置禁止布线层,防止晶振电路上铺铜

- 禁止区域-多层(包括顶层/底层);禁止选项-铺铜

3W:W是单个线的宽度,3W是指两条线的中心间距要大于3倍的线宽

PCB布线要尽量远离空安装孔、电路板边缘

- 避免PCB钻孔加工中,切掉一部分导线

需要添加泪滴

椭圆形/条形的焊盘,建议从短边引出线,避免在焊盘处形成直角

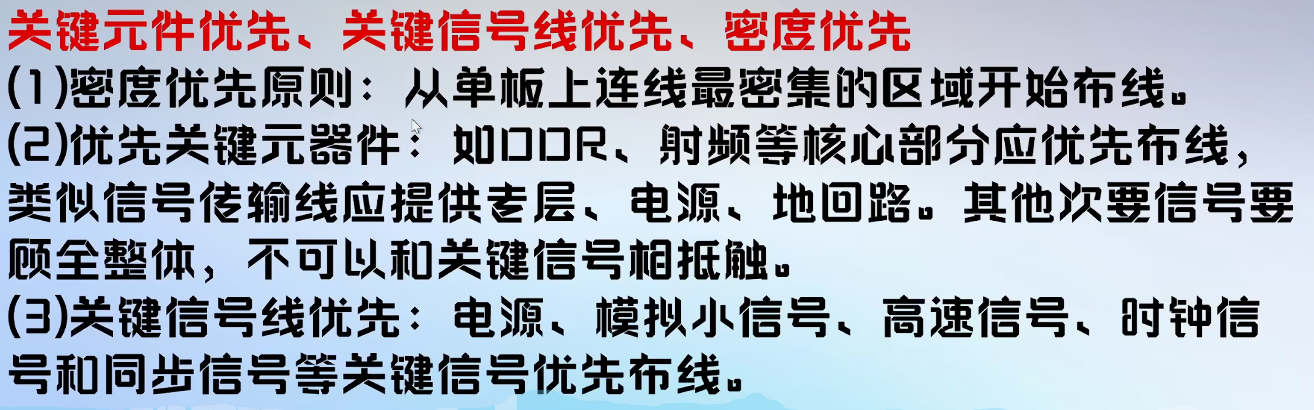

布线顺序

- 关键元件优先、关键信号优先、密度优先

快捷操作

嘉立创

sh框选器件后 按command + shift + x # 布局传递,将原理图的布局应用于PCB布局 框选器件后 按shift + x # 跳转到原理图/PCB,并高亮选中部分1

2sh设置-PCB/封装-常规-布线-自动添加泪滴 # 布线时自动添加泪滴1

EDA软件

Electronic Design Automation,电子设计自动化软件,用于电子系统设计、仿真、分析、布局、布线、验证和制造准备的计算机程序集合。

- 常见

- Altium Designer

- KiCad 开源免费

- 嘉立创EDA

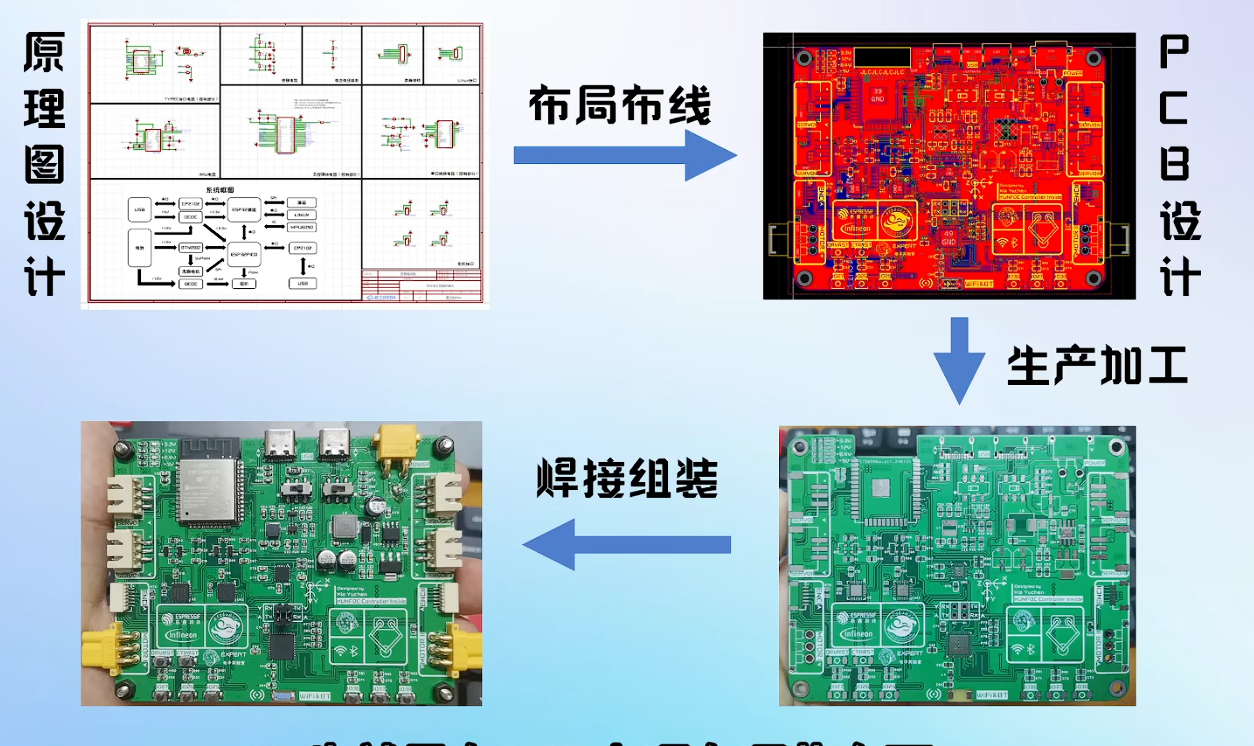

- 流程:原理图设计 - PCB设计 - 打样 - 焊接 - 功能验证

- 原理图四要素

- 元件符号

- 连接线

- 结点

- 注释

嘉立创EDA

浏览器:在线版与本地版

- 在线版只能通过网络操作,对团队协作友好

- 本地版既能网络也能离线,团队协作不太友好

APP

- 全在线模式:均保存在服务器

- 半离线模式:工程和库保存在本地,支持使用在线系统库

- 全离线模式:均保存在本地,不支持使用在线系统库

设置 - 保存

- 开启自动备份

- 开启自动保存

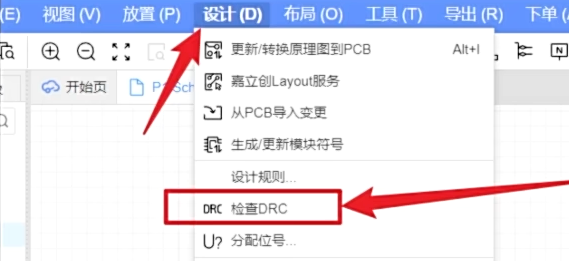

原理图DRC

Design Rule Check 自动化检查过程,EDA通过一定的规则设定检查原理图或PCB设计。确保符合特定规范或指导标准。

- 标准来源:设计-设计规则

- 检查与案例图 / PCB

下单

- PCB下单

- 下单前可在官网尝试领券,免费打样等

- 元件下单

- 器件标准化检查-对比嘉立创商城是否存在匹配元件

- 修改元件位号/名,也会导致不一致,但不影响,供应商编号一致即可

- SMT元件库

- SMT基础库 元件默认再流水线,下单帮安装更便宜

- SMT扩展库 当让嘉立创平台焊接时,需要人工换料价格会更贵(普通下单不会额外收费-与基础库一致)

- 器件标准化检查-对比嘉立创商城是否存在匹配元件

- 产生三份文件

- 坐标文件:一般是PCB上要打的孔

- Gerber文件:涉及PCB上的导线、丝印等

- BOM文件:物料清单,记录PCB需要用的电子元件种类及数量

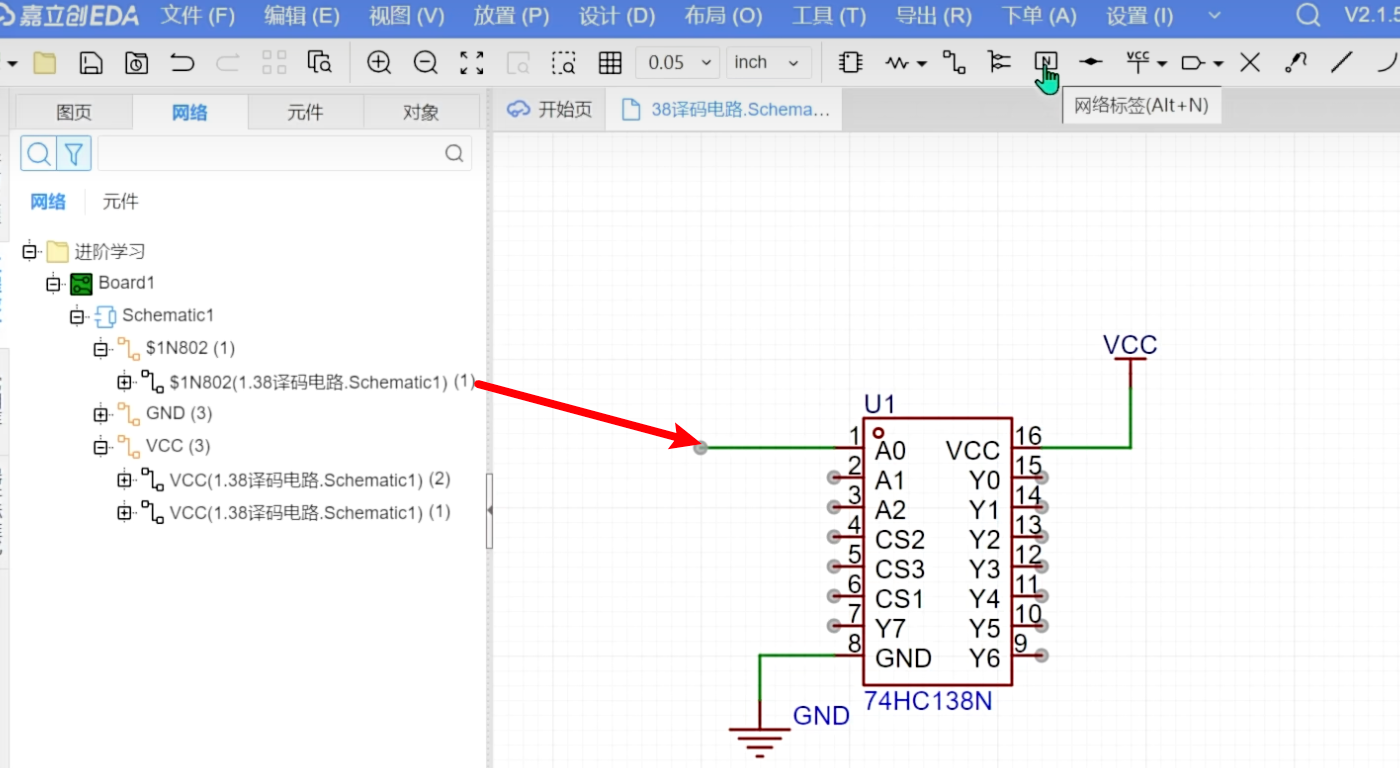

网络

- 同一网络标识的引脚,表示连接在一起

- EDA会为每根引脚设置默认网络,除非用户指定,也可通过放置网络标识到导线上进行修改

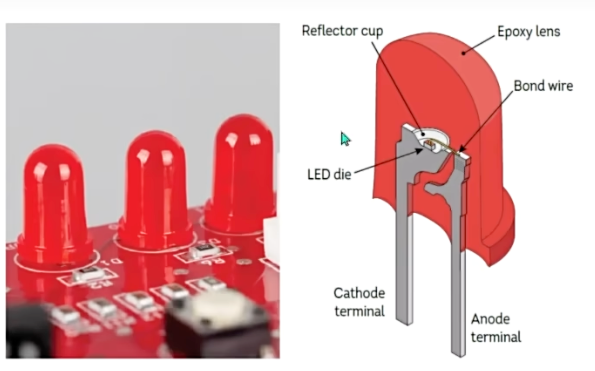

常见器件

USB接口

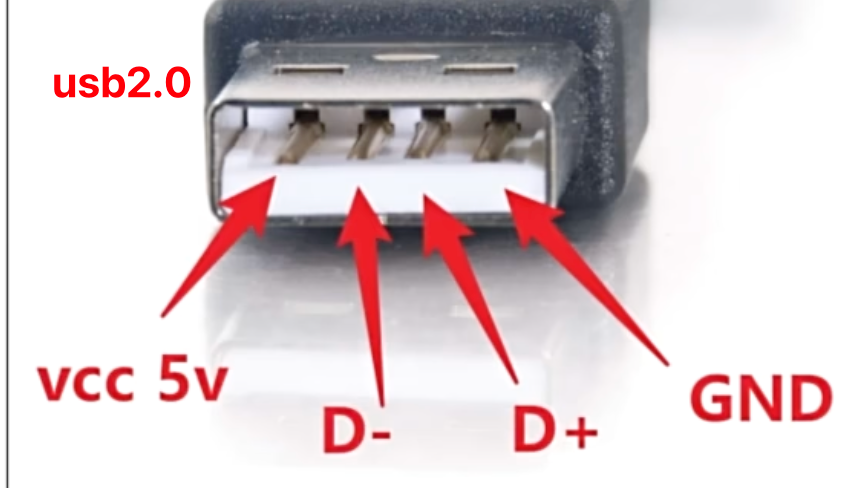

micro usb接口属于 USB(Universal Serial Bus 通用串行总线)协议,规定了USB有几根引脚,每根引脚从左至右分别的功能

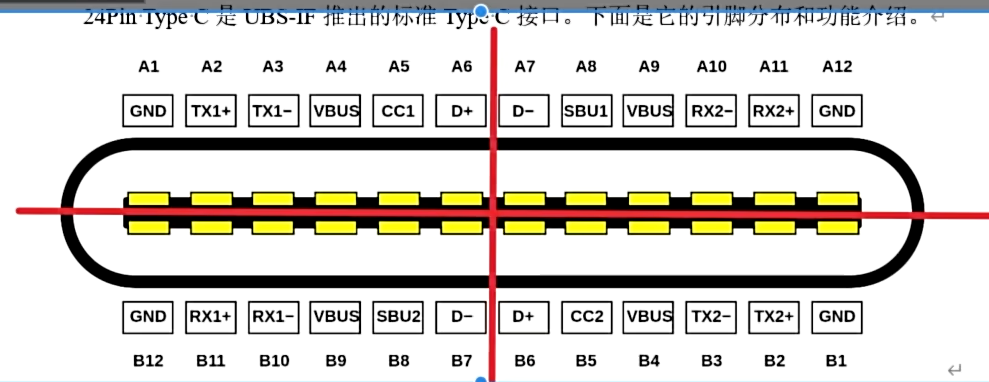

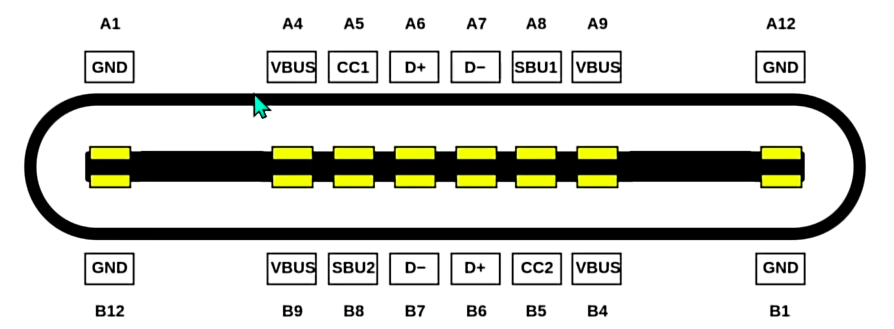

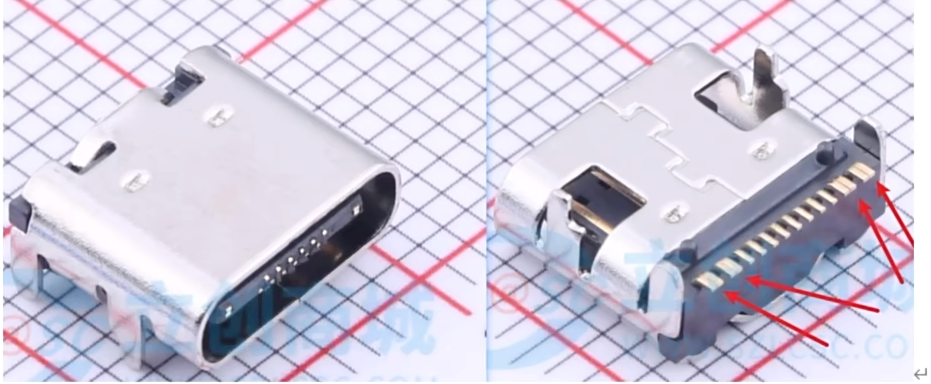

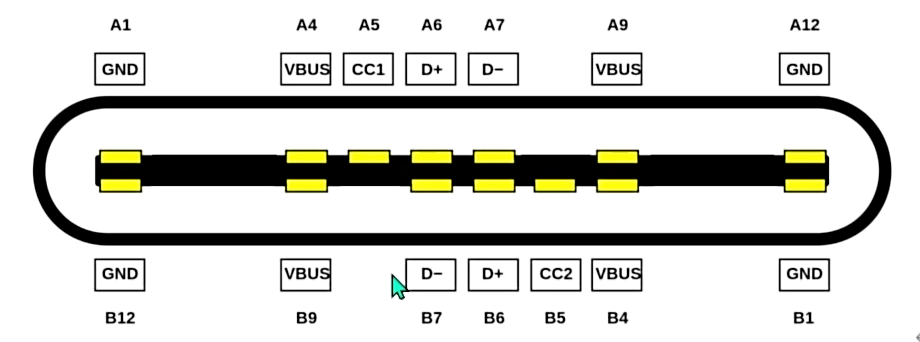

TypeC

接口选型

- 对角对称结构,使其不用区分正反,根据内部交互协议实现主从控制

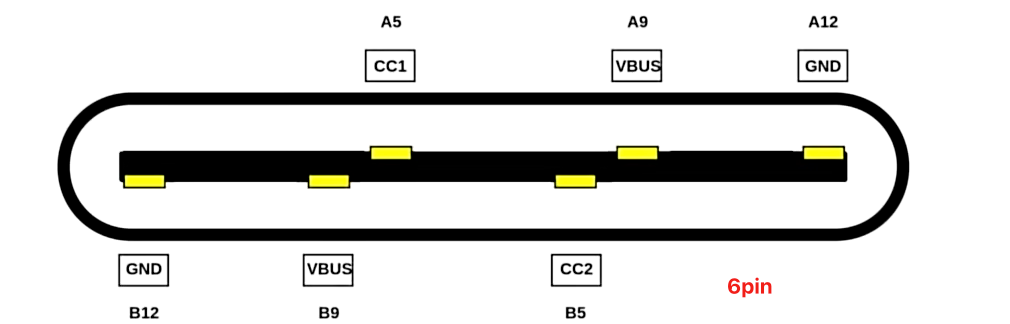

- 分类

- 24pin 标准接口,功能丰富

- 16pin / 12pin 移除高速数据传输的TX引脚,只能是USB2.0的速度,依旧支持音视频、PD快充,省钱

- 14pin 砍掉音视频传输接口,成本降低不明显,不常见

- 6pin 仅保留供电能力,适合做低功率供电

| 标识 | 含义 | 备注 |

|---|---|---|

| A1、A12、B12、B1 | GND | 接地 |

| A2、A3、A10、A11、B11、B10、B3、B2 | TX、RX | 差分信号对,实现高速数据传输 |

| A4、A9、B9、B4 | VBUS | 电源正极 |

| A5、B5 | CC1 | 连接时判断索要电源/给别的设备充电 也可用于协商冲电协议,识别正反插等 |

| A6、A7、B7、B6 | D+(DP)、D-(DN ) | USB2.0数据传输 |

| A8、B8 | SBU1、SBU2 | 传输视频/音频信号 |

充电协议

提升电流/提升电压,但市面大多数线材设计都是用 5A设计,设计过大电流不安全

- 传统USB供电协议

- 【USB 1.0-2.0】 最大电流 500mA 电压5V

- PD协议

- 电压:5、9、15、20V

- PD3.1支持 28、36、48V

- 最大电流:5A

- 最大功率:100W(PD3.0),240W(PD3.1)

- 电压:5、9、15、20V

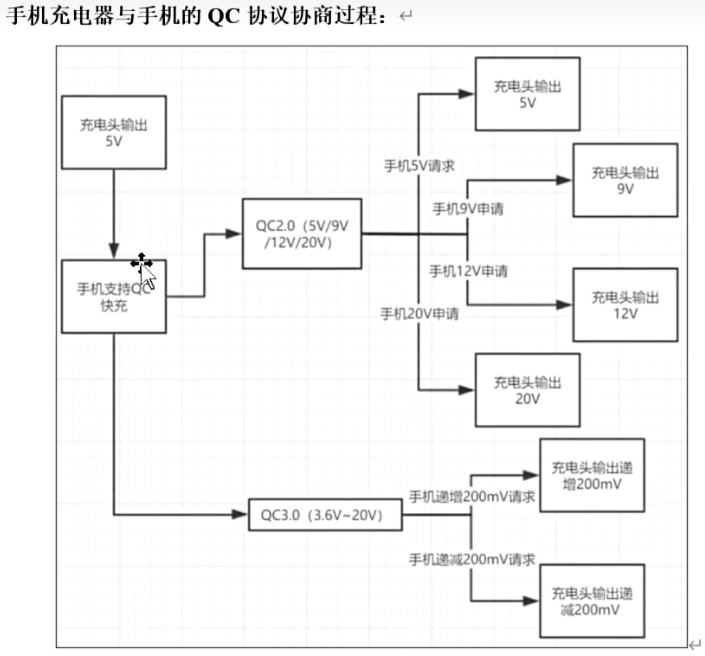

- QC协议

- 高通开发的快充协议,每个版本支持的电压电流不太一样

- QC 2.0

- 最高电流 3A

- 电压 5、9、12、20V

- 最大功率 18W

- QC 3.0

- 最高电流 3A

- 电压 3.6-20V(动态调整)

- 最大功率 24W

- QC 4.0/4+

- 最高电流 3A

- 电压与USB·PD兼容,支持5、9、12、20V

- 最大功率 100W

快充协商过程

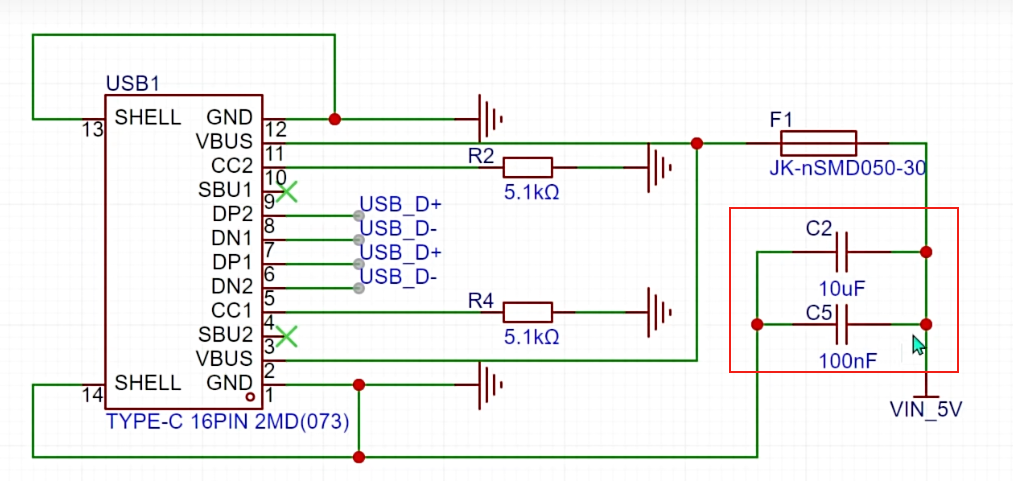

- 初始连接 5V 标准电压供电【CC1 CC2 引脚】

- 充电头通过CC引脚检测连接的设备类型和方向

- 专用快充协议协商芯片

- 受电设备通常有专用的快充协议协商芯片,复制通过CC引脚与上游设备进行通信

- 协商芯片在接收到5V供电后,与上游设备进行通信,协商所需的更高电压和电流

- 芯片如:USB·PD控制器、Qualcomm·Quick·Charge控制器

- 通信与协商

- 协商失败处理

- 下游设备不支持快充协议或通信中断,充电头会继续维持初始5V供电

关键部分

滤波电容

- 经验取值100M以下晶振:10uF-应对低频干扰 100nF-应对高频干扰

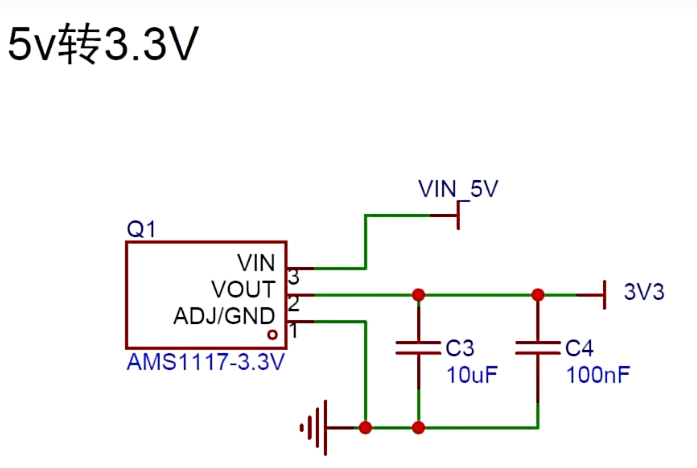

线性稳压器LDO

- 低压差 18-4.5V转3.3V

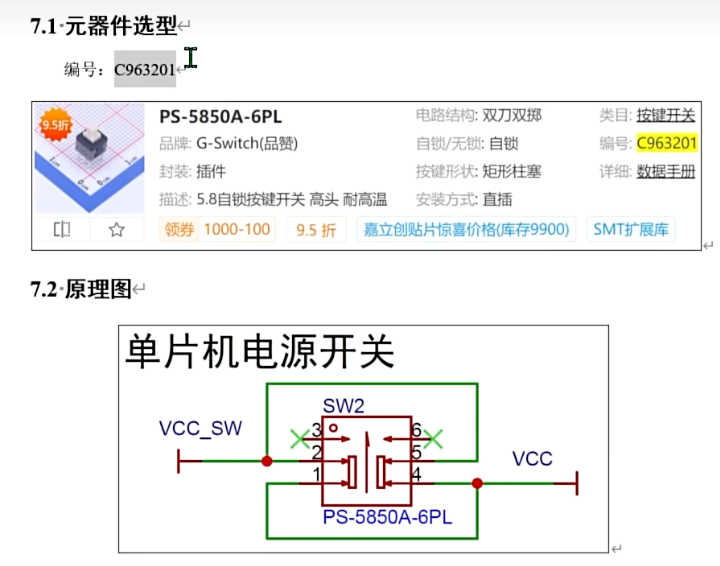

电源开关

- 自锁开关

其他保护电路的部分

- 保险丝

电压标准来源

- 早期 mos管为主的半导体电路,为保证供电5V才能使用,5V成为行业标准

- 随着半导体制造工艺发展,芯片可在更低电压下运行,显著较少功耗和发热;尤其是现代高性能计算设备中,CPU和内存条通常使用1V左右电压即可

- 3.3V在嵌入式设备的应用,制作成本和功耗的平衡点

开关类

自锁开关

- 说明:按下后松开,不会自动弹起,如圆珠笔的开关

保险丝

- 传统保险丝:使用易熔断材料,一次性

- 当电路出现过载或短路时,电流突然增大,保险丝受热膨胀导致断流,切断电路

- 自恢复保险丝/自复位保险丝/PTC保险丝:重复使用

- 通常由 聚合物和导电颗粒(如碳黑或金属)组成

- 正常电流下,温度稳定,电阻较低,电流自由流动

- 过载条件:电流增加,保险丝过热,聚合物基质膨胀,内部导电颗粒间距增加,断开部分电流路径

- 高阻态:随着电流路径断开,电流减小,有效方式电路过载受损

- 冷却与自恢复:电流过载消除并降至正常水平后,保险丝冷却,聚合物自动收缩,电流路径重新建立,恢复正常

- 关键参数

- 保持电流:正常电流

- 跳闸电流:进入高阻值状态的电流

排针

外部晶振

元件选型

- 封装规格【长宽-英寸单位】

- 注意

- 电阻的高度基本保持一致,电容的高度差异明显

- 大容量电容放在小封装规格,会损失精度等

- 不建议选择 封装0201及以下的,太小不好焊

- 常见

- 0201

- 0402 表示4*2英寸大小

- 0603

- 0805

- 注意

电阻元件

| 贴片元件 | 插孔元件 | |

|---|---|---|

| 体积重量 | 小 | 较大 |

| 批量生产成本 | 低 | 较高 |