数字电路

本篇截止目前仅考虑可用性,暂不考虑电路优化,因此不一定时最优

基础入门

二进制

- 通讯系统有 编码 和 解码 另个过程

- 早期为实现低成本通讯,引入【时序】概念,如 摩斯密码,亮几秒灭几秒

- 嵌入式中,硬件间为了少连线,也会采用时序的方式发送信号

- 表示一切

- 文字:常见编码 ASCLL码-8Bit GBK-16Bit加入繁体 utf8/unicode-1B->4B

- 图片:像素化、像素数字化;分小格-表示小格的颜色;RGB、RGBA表示

- 声音:采样率、量化;常用采样率44100HZ、48000HZ;量化-振幅高度-位深-一般16bit或24bit

- 视频:由图片与声音结合,类似帧动画;常见编码标准 H.264、H.265、AV1

- 位 bit

- 二进制中每位 bit 都是 0 或 1

- 一般用b表示,如 8b 表示 8位 8bit

- 计算机中最小数据单位

- 字节 Byte

- 8bit 组成一个字节,2的8次方共 256 种状态

- 一般用B表示,如 5B 表示 5个字节

- 其他计量单位

- 1K = 1024B 2的10次方B

- 1M = 1024K 2的20次方B

- 注意

- 生活中 100M宽带 指 100M bit

- 而内存中说 100M内存 指 100MB = 100*8M bit

数字电路

信息数字化后,可用二进制便捷的表示信息。数字电路就是研究如何用电表示二进制。高电平表示1,低电平表示0。

逻辑门电路

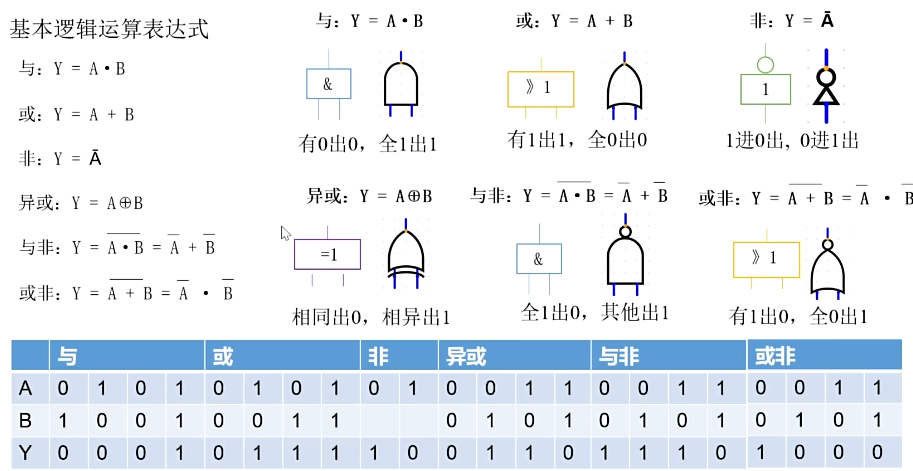

基础门电路

- 与门:两个输入都为高时,输出高,否则输出低

- 或门:两个输入,相同输出高,不同输出低

- 非门:输入高,输出低;输入低,输出高;可用继电器实现

扩展门电路

可由基础的三个门电路组合构成

- 异或门:两个输入,相同输出为低,不同输出为高;奇数出1,偶数出0

- 与非门:全1出0,其他出1

- 或非门:有1出0,全0出1

- 异或非门:相同出1,相异出0

运算器

加法

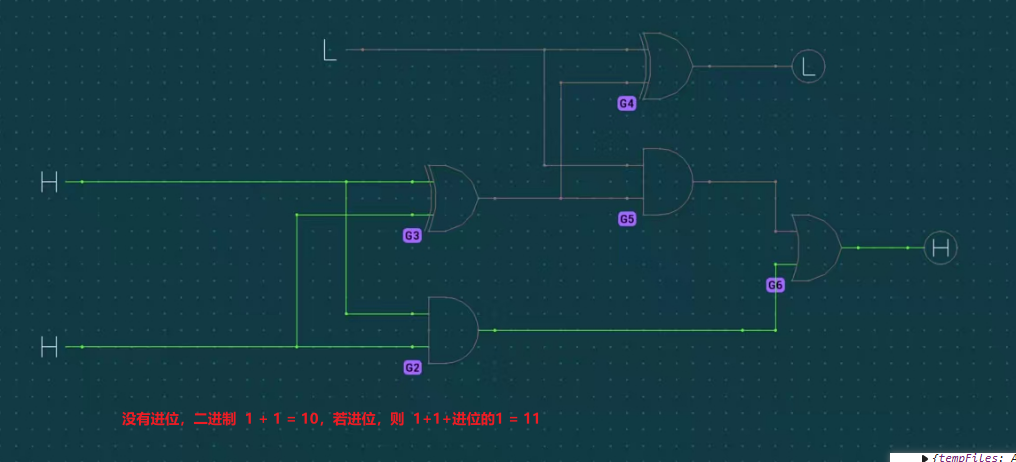

半加器 - 不考虑进位情况下,实现1位加法运算

- 利用门电路实现

1位加法器 - 考虑进位情况下,实现1位加法运算

- 利用门电路实现

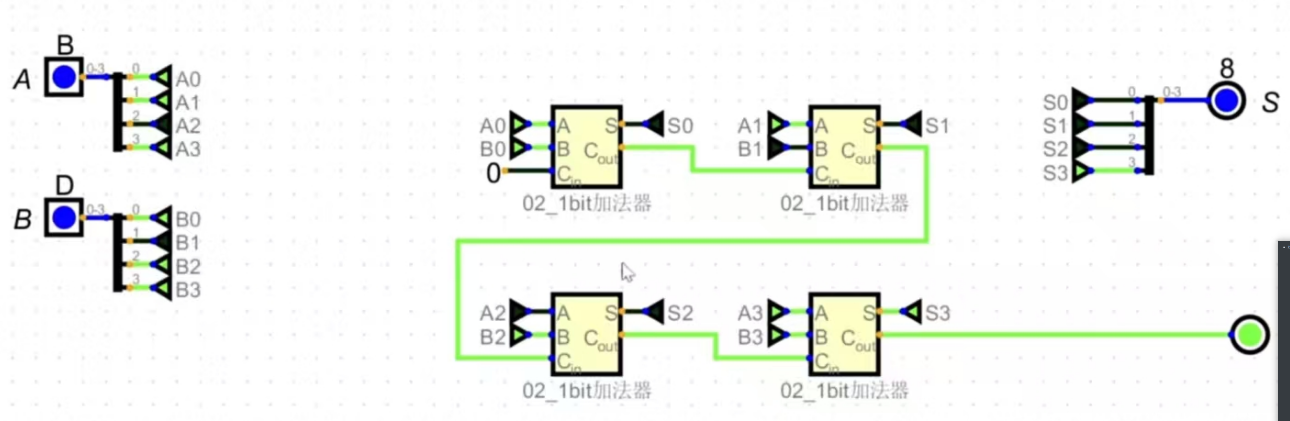

多位加法运算器

- 使用多个全加器,实现多位的加法运算

- 三角形 - 隧道:实现同名隧道间互相连接,便于画示意图

- A 代表着4位的输入,分别是A0、A1、A2、A3

减法

- 半减器

- 1位减法器

- 多位减法器

锁存器与触发器

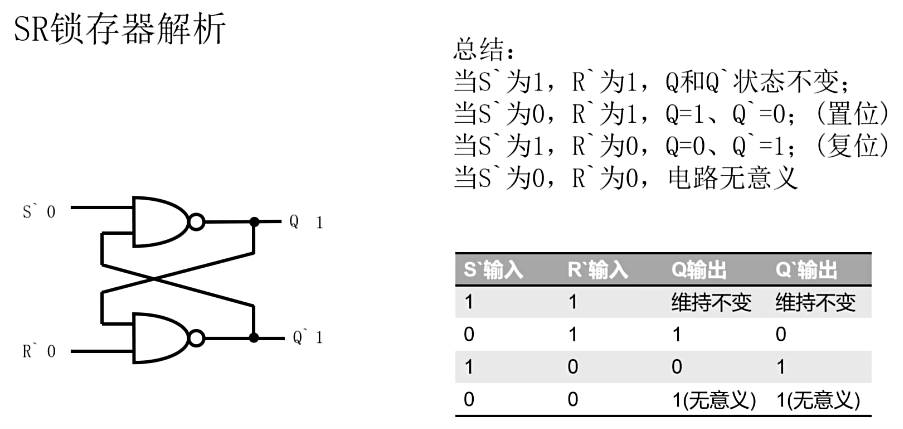

两个与非门

- 两个高电平 输入时为初始状态,两个输入一致时表示未启用

- 变换某个输入电路的输入时,更改存储的数据0/1

- 两个输入分别为 置为、复位

两个或非门

- 两个低电平 输入时为初始状态,两个输入一致时表示未启用

- 变换某个输入电路的输入时,更改存储的数据0/1

- 两个输入分别为 置为、复位

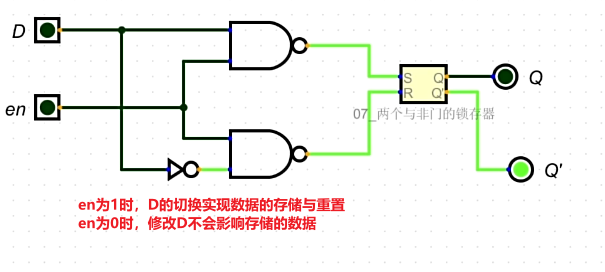

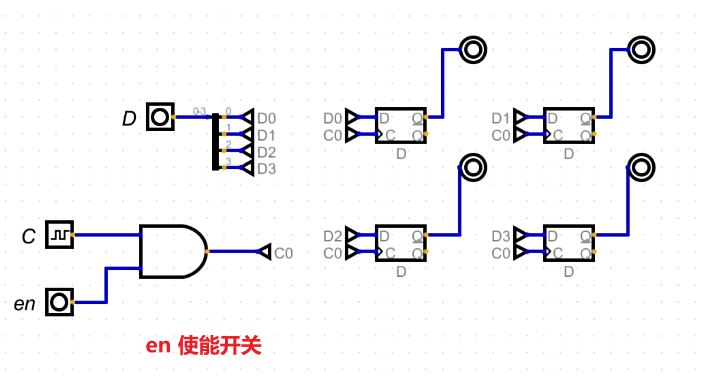

带en开关的SR锁存器

带en开关的D锁存器

优化省略,R复位输入控制

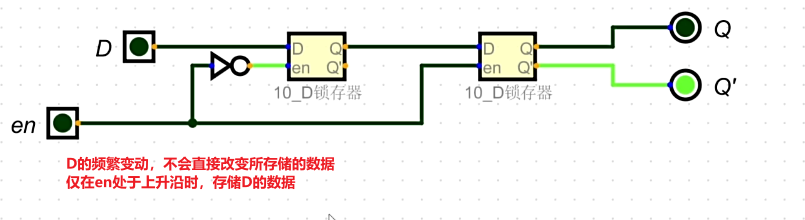

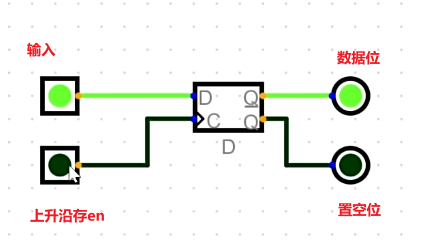

D触发器

仅在en的上升沿瞬间,发生数据的变化,从而避免D的不稳定,导致数据异常变化

- CPU中数据处理速度,由en上升沿变化速率决定,因此本质受时钟频率控制

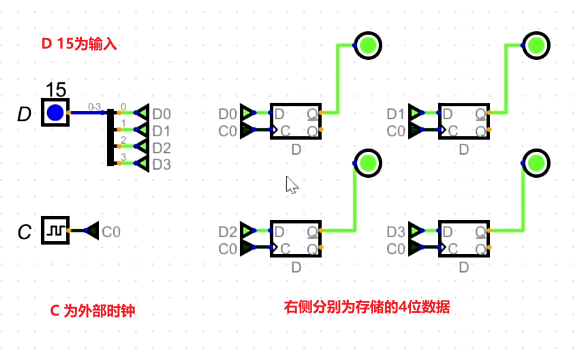

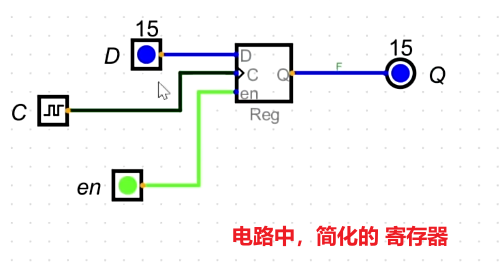

4位寄存器实现

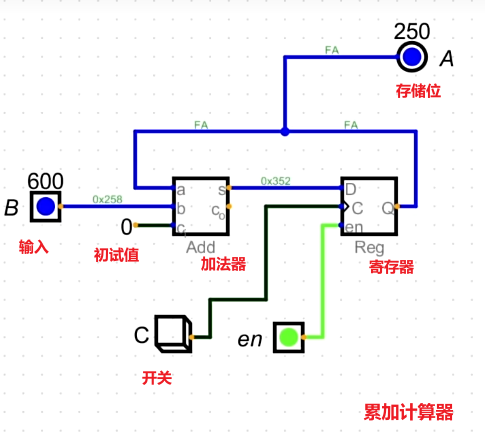

累计计算器

- 按下开关C时,执行一次运算

计算机组成原理

冯诺依曼模型

基于通用图灵机建造的计算器都是在存储器(内存/寄存器)上存储数据,鉴于程序和数据逻辑上都是相同的,因此程序也能存储在计算机的存储器中。

- 冯诺依曼的四个子系统

- 存储器:用来存储数据和程序的区域

- 算数逻辑单元(ALU):进行计算的地方(算数运算、逻辑运算、位运算等)

- 控制单元:对存储器、算数逻辑单元、输入输出等子系统进行控制操作

- 输入/输出单元

- 输入子系统:负责从计算机外部接收输入数据

- 输出子系统:将计算机处理结果输出到计算机外部

- 主要概念

- 存储程序

- 程序必须存储在存储器(内存)中,意味着程序和数据应具有相同的格式,实际都以位模式(0、1)存储在内存中

- 指令的顺序执行

- 程序由一组数量有限的指令组成

- 控制单元从内存中提取一条指令,解释并执行指令;一条一条按顺序执行

- 存储程序

组成部件

三大部件:中央处理单元-CPU 主存储器-内存 输入输出子系统

中央处理单元CPU

- 分类

- 算数逻辑单元

- 控制单元

- 寄存器组:存储临时数据的高速独立存储单元

- 数据存储寄存器:保存运算的中间结果

- 指令寄存器IR:CPU从内存中逐条取出的指令,在这里解释并执行

- 程序计数器PC:保存当前正在执行的指令地址,执行完成时,计数器自动加1,指向下一条指令的内存地址

- 概念

- 内存集成到CPU中,能带来更高的性能、更低的功耗和更小的物理尺寸。

- 苹果、英特尔、AMD和台积电等厂商均有使用

主存储器 内存

- 存储单元的集合,每个存储单元都有唯一的地址标识

- 数据以“字”形式,在内存中传入传出,一般为8位,1字节

- 内存类型:RAM、ROM

- 随机存取存储器 RAM

- 断电后数据/程序丢失

- 只读存储器 ROM

- 断电数据不丢失,其中部分为制造商写入禁止随意修改的区域为系统盘

- 随机存取存储器 RAM

- 概念

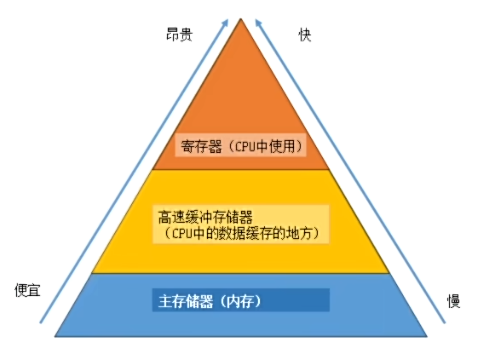

- 高速缓冲存储器

- 存储数据比内存快,比寄存器慢,容量较小,被置于CPU和主存储器/内存之间

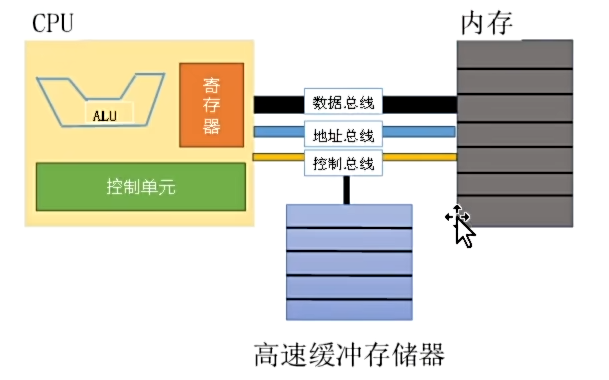

- CPU和存储器的连接

- 通常由三组线路进行连接,统称为总线:数据总线、地址总线、控制总线

- 数据总线:多根线组成,每根线每次传递1个位的数据;例32位计算机则拥有32根数据总线

- 地址总线:地址总线的线数取决于存储空间的大小。存储容量为2的n次方个字,那么地址总线一次需要传递n位的地址数据,因此需要n根线

- 控制总线:负责传送指令。计算机有2的m次方条控制指令,那么控制总线就需要m根

- 高速缓冲存储器

输入输出系统

- 分类

- 非存储设备:键盘、鼠标、显示器、打印机

- 存储设备/辅助存储设备:通常为 磁介质、光介质两种

- I/O 设备的连接

- 输入输出设备不能直接与CPU和内存的总线进行连接,本质上IO设备都是磁性或光学设备,比CPU电子设备慢的多。因此需要介质 I/O控制器 处理这种差异

- I/O控制器

- 连接输入输出设备到总线,每个I/O设备都有一个特定的控制器

- 分类

- 串行控制器:只有一根数据线连接在设备上

- 并行控制器:多根线连接在设备上,能同时传递多个位

- 常用控制器:SCSI、火线、USB、HDMI

程序的执行

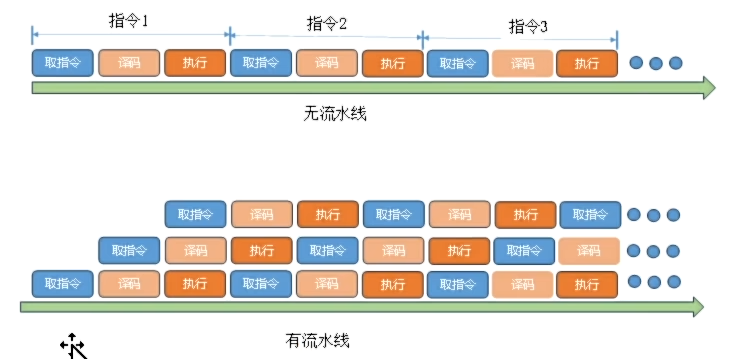

- 机器周期

- CPU利用重复的机器周期来执行程序中的指令,一步一条,由开始到结束

- 一个周期包含:

- 取对应地址指令 ->

- 译码【产生系统可执行的二进制代码】 ->

- 执行

体系结构

CISC 复杂指令集计算机

- 设计策略:使用大量指令,包含复杂指令

- 优点-程序易设计;缺点-指令集、电路复杂

- 优化方案:CPU不直接执行机器语言指令,只执行复杂指令转化后的一系列微操作【微程序设计】

- 应用:英特尔开发的奔腾系列CPU、i3-i7-i9

RISC 精简指令计算机

- 设计策略:使用少量的指令完成最少的简单操作

- 缺点:程序设计更难,复杂指令需要用简单指令模拟

- 应用:ARM、苹果M1、M2、高通、骁龙

流水线【多线程】